Quoting from Dally and Poulton:

“A synchronizer is a device that samples an asynchronous signal and outputs a version of the signal that has transitions synchronized to a local or sample clock.”

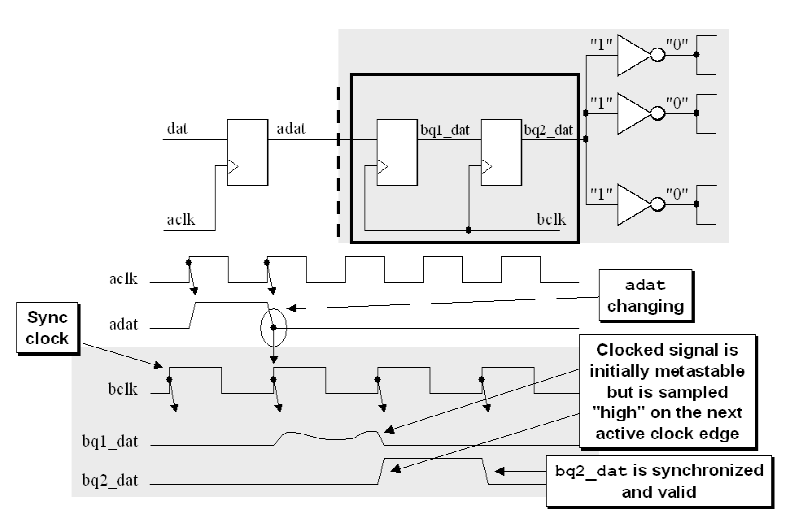

🧩 The Two-Flip-Flop Synchronizer

The two-flip-flop synchronizer is the simplest and most widely used synchronizer design in digital systems.

🏗️ How It Works

-

Stage 1:

- The first flip-flop samples the asynchronous input signal into the new clock domain.

- It then waits for one full clock cycle to allow any metastability on the stage-1 output to decay.

-

Stage 2:

- The second flip-flop samples the stage-1 output using the same clock.

- The output of the second stage (stage-2 signal) is expected to be stable and synchronized, making it safe for use in the new clock domain.

⚠️ Residual Metastability

- It is theoretically possible that the stage-1 output remains metastable when the second flip-flop samples it.

- In such cases, the stage-2 output could also go metastable — though this is highly unlikely.

🧮 Mean Time Between Failures (MTBF)

The probability of synchronization failure (i.e., metastability propagating through both stages) can be described by the Mean Time Between Failures (MTBF).

MTBF depends on several factors:

- The frequency of the input signal,

- The clock frequency of the receiving domain,

- The resolution time allowed for metastability to settle, and

- The characteristics of the flip-flops used.